Hello, I'm new to Cadence, coming from Altium. I'm using Allegro Design Entry HDL and PCB Editor, rev 16.3.

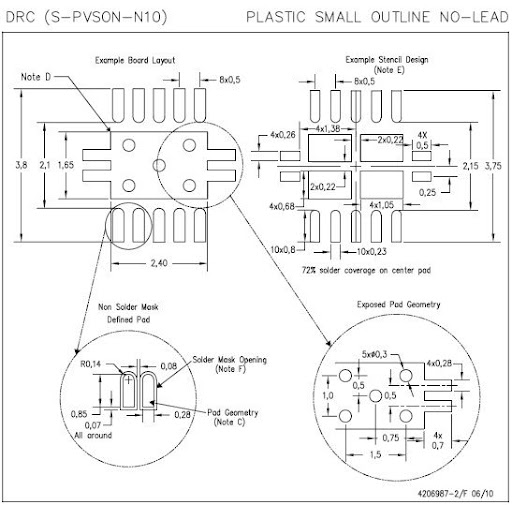

As part of the new design and "new to designing with Cadence" process, I am creating parts for our library and I'm having some trouble with a TI SON part that includes a thermal pad or power pad. Here is a snap shot from the TPS6120:

At this point, I've made the pads in the padstack editor (but made them rectangles since I didn't know how to make it a rect at one end and rounded at the other) and used the symbol creation wizard to make a SOIC. To make the thermal pad I placed a filled polygon on the Etch/top layer and it is one large pad with the outline like above.

Question: How do turn my filled polygon into a ground pin (or should I not?) and how do I add the soldermask layer to something I've drawn like this?

Question: How do I add vias to my footprint? My plan was to create the via in the padstack editor then place them in the appropriate places but I have some confusion as to whether the pad/via structure is just supposed to sit there dangling or if it should be assigned a pin # (ground).

I did search the forum and came across the thread Thermal Pad Shape with Vias In it a poster mentions that he makes these pads using multiple surface mount style pins. I think I can figure out how to do this but I'd appreciate any tips on setting up the tools and pads so that things are properly done.

Picture of the pad made from pins: