Hello everyone

I cannot make this work, can you please help me undersatand if there is a way?

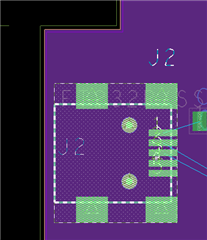

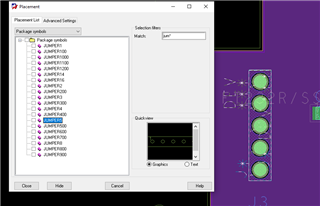

I'd like to ignore a hyerarchical object on a Schematic Page from routing on PCB Editor.

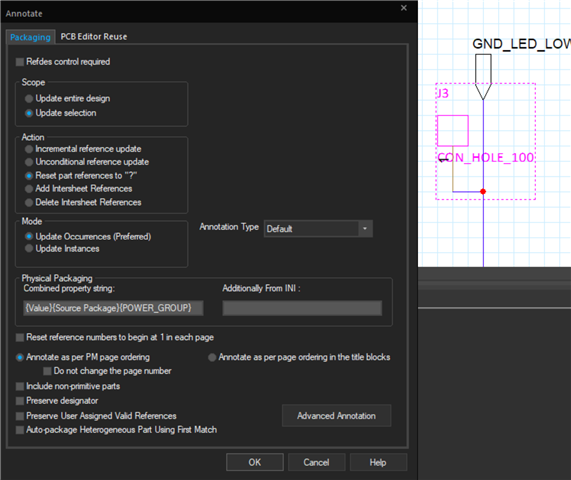

I have tried setting the NETLIST_IGNORE to TRUE for the hierarchical object, but DRC shows me that its elements are still being considered - the problem is there are situations where only one block instance should be excluded - besides that, selecting all the sub-components and setting the property is not as handy, obviously.

Is there a way?

If I go and set the NETLIST IGNORE for all the components in the block to true, they are being excluded as expected, of course.

Thanks