I've gotten the following error when generating a netlist on a schematic. It goes away if I delete the part in question, but comes back if I add that part back to the schematic. An earlier version of the schematic with the same part goes through the netlist creation without any errors. Any idea what is causing the problem?

Thanks,

John

(project name/path and part name replaced with generic names to remove proprietary information)

Loading... C:\...\ALLEGRO/pstxnet.dat

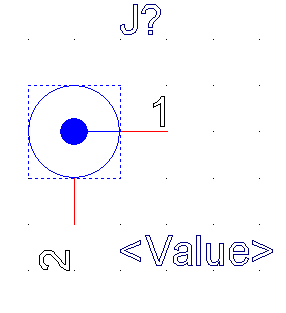

packaging the design view...#228 ERROR(SPCODD-228): Cannot package the following primitive instance in any section of the physical part 'MOSFET_PACKAGE_MOSFET'.

Primitive Instance: @\schematic post review\.schematic1(sch_1):ins2777027@orcad_parts.\MOSFET.normal\(chips) (MODULE: SCHEMATIC POST REVIEW; PART: MOSFET)

The primitive instance has pins which does not match the section definition in chips.prt. Check the pin definitions for each section in the chips.prt file. Regenerate the netlist and rerun packager.

#53 ERROR(SPCODD-53): Packaging cannot be completed because packaging has encountered a null object ID. The design may not have been saved correctly. Save the design before packaging.

ERROR(SPCODD-391):

Reference Designator: Q201. Could not pack schematic instance @\schematic post review\.schematic1(sch_1):ins2777027@orcad_

parts.\MOSFET.normal\(chips) (MODULE: SCHEMATIC POST REVIEW; PART: MOSFET) in sections.

#53 ERROR(SPCODD-53): Packaging cannot be completed because packaging has encountered a null object ID. The design may not have been saved correctly. Save the design before packaging.

![]()