Hi

I had run DRC on my design and have got some markers here and there.

Now i am trying to remove these markers which I am unable to do. It worked fine on 17.2 release. Settings are:

Hi

I had run DRC on my design and have got some markers here and there.

Now i am trying to remove these markers which I am unable to do. It worked fine on 17.2 release. Settings are:

Hello All

Greetings..

I have designed a PCB with the components on both TOP and bottom layer . Generated OBD++ and pick/place file. But the Assembly house is reporting that the ODB++ file generated from PCB is showing that all the component location is TOP on their tool (CAD CAM Professional). where as the pick/place file shows the bottom components correctly as "m" orientation.

Not sure why the OBD++ file is showing wrong positions. Kindly help.

Tool: PCB Designer professional 16.6 ( with ODB++ inside)

Regards

Pradeep

Hello Everyone, I would like to change the property "Package to Package Spacing" from 0 to 0.5 mm. I know it exists (see pic) but i cannot manage to find how to modify it. Please, someone could help me ?

Orcad 17.2-2016 S047 Standard licence

Best regards

Hello, I am using Orcad Capture CIS 17.2

I have been trying to make a custom Filter in Properties Editor->Parts tab.

I am able to Hide the columns I don't need, and Add Filter for columns I do need.

What I am unable to do, is rearrange the columns to make is simpler for me to see all the information I want . For instance I want the Part Reference column to be second in the Properties window.

I can highlight the whole column, hover the mouse until the small gray rect appears, then hold LMB and drag across the other column headers. A red line appears between each column as I move . When the red line is in the position I wish to move the selected column, I release LMB and I see a flash of the column contents move, but the column just remains where it started. It doesn't matter what direction I am rearranging, or the type of column (Orcad built in or a custom New Filter column).

It almost acts like when the Windows desktop is locked so you cannot rearrange Icons.

Is there a setting or entry in an environment file that would be causing this?

So , many of the basic tasks in Orcad Capture CIS have proven to be very frustrating. In this instance, adding a border to my schematic pages

I know that there is a border feature in ORCAD Capture CIS, because in Schematic Page Properties, there are Grid Reference Options

I have searched online and through these forums, but cannot find an answer. When I use ORCAD's Help and search, I don't get any responses that refer to Capture CIS.

And the Allegro HDL Design Entry Instruction don't match what is in Capture CIS Toolbars and Options

Capture CIS doesn't have a Component-Add function, or a Part Manager Window and there is no Standard Library that I can find

In the Capture User Guide and Help, there is nothing about borders

Can anyone here provide me some guidance to where these tasks are explained?

Thanks

Hello,

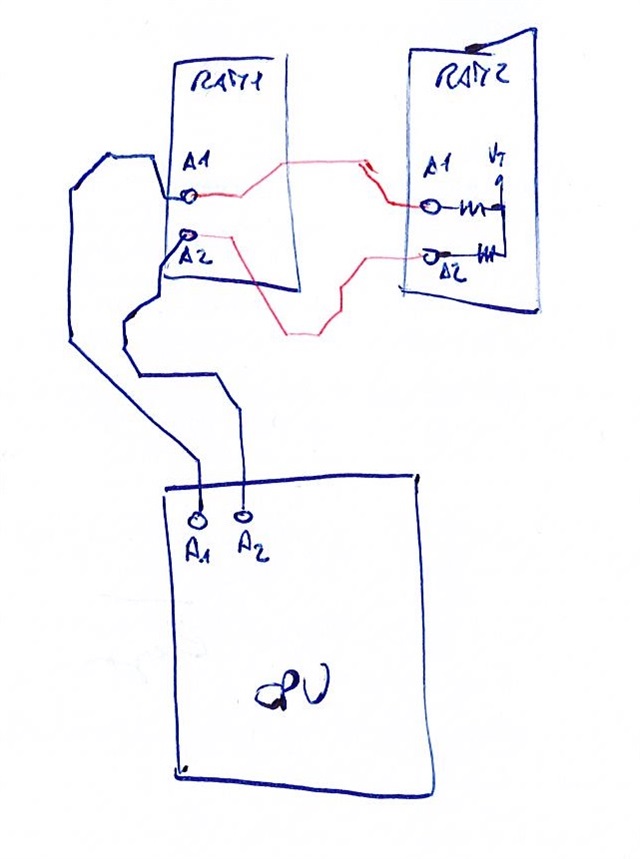

I'm relative new in Orcad and I'm working on a board with two DDR3 RAM.

Address lines have flyby termination, so I've to route traces from CPU ball to first RAM then to second one and at last to the resistor.

Here you are a hand made diagram with two lines routed

At the moment address lines are in one Match Group but this is not the right rule. I need to setup a rule like this

In Mentor programs there's Virual Pin objet for this rules but in Cadence I'm not skilled

Can anybody help me?

Thank you

Stefano

I am attempting to get title blocks to work in my designs, but they do no behave how the help and tutorials say they should.

When I start a new design, and fill in the Title Block tab of the Design template

And then place a title block from the Capsym library

The result is an incomplete Title block with nothing automatically filled in. The Title , Organization Name and Rev should be filled in because they are fields in the Design Template ->Title Block

Other than clicking on each title block on each sheet and editing fields, the only way I have found to edit the Title blocks is to use Edit -> Browse - > TitleBlocks and then use the properties editor to make changes.

This is really inconvenient because there are 20+ fields of unhelpful information which cannot be hidden or arranged for clarity

This shouldn't be so difficult. Why doesn't the standard built in Title Block , located in Orcad's provided Libraries , auto fill in the information I provide for my design?

Thanks

Hi

What are the features of Cadence 17.4 Allegro over than 17.2?

What's a good method to insure a component (using place boundary extents) is not placed on top of a through-hole pin?

Example: connector on top side of board, SMT part under it on bottom side of board.

I'm considering adding place bound bottom shapes to through-hole pins but there must be an easy way I'm missing.

Thanks

Hi

Is the Routing for breakout both ends is possible for Cadence 17.2 Allegro?and how to route trunk route in Cadence 17.2 Allegro using Licence below

* Allegro_performance

* Allegro_studio

* PCB_design_studio.

Hi all,

I imported a dxf file and various line element groups were made from the dxf file. As you can see from the image, the yellow arrows represent a complete element group that was created. It is only a collection of segments as seen in the box pointed to by the pink arrow. The image also shows a fuchsia line pointed to by the green arrow. This line does not exist in that group of lines. I made the line by snapping it to the vertex of the connecting grouped lines.

Is there a way to make a new element group so I can z-copy that specific shape to the top etch layer? I need this help because when I made a shape from a group of line segments pointed to by the orange arrow, it messed up my dynamic shape plane as you can see from the black void (labeled void) inside that highlighted line group.

Any Help would be greatly appreciated.

Hello,

I'm using Orcad 17.4 and my PDF export is acting strange - no nets, or components values apear on the output file.

I'm using gswin64c converter

For exampe:

I have created a pcb design in orcad 17.2 the schematic is now converted to board using layout now I have to compare and cross check the nets of schematic vs netlist vs layout in orcad there is a method called inter tool communication but it highlights every net we click to schematic to corrosponding in layout it takes too much time to compare each net is there any faster method to compare both nets schematic vs layout in faster way?

HI,

is it possible to use box / rectangle select in HDL to crossprobe and select multi components in PCB Designer at once?

I can ctrl+left click multi components one at a time in HDL and than use move command in PCB Editor but I can't box select.

If I set the filter in HDL to only symbol, box select and then use highlight in HDL, I see in the PCB Designer console output that the parts are first selected and then highlight, so the functionality to cross select multiple components at once exists.

Thanks

Nicolas

I'm designing a daughter board using OrCad Layout (old, I know). The board has 2 40 pin connectors at opposite ends. Both connectors have VCC net connections to the main board. The main board has the power supply and supplies VCC to multiple pins on each connector. I routed the board to use the closest VCC pin on a connector.

The issue I am having is that when I check connectivity, it shows all the VCC pins on each connector not being connected to each other as they are actually connected together on the main board. Short term, I added routes to all the VCC pins between the 2 connectors so I can check to see if I'm missing any other connections. I would rather not leave the connections there.

The question: Is there a way to indicate that multiple pins are connected externally from the PCB so Layout doesn't show them as being disconnected?

Hi

I am drawing a qfn.dra file. The 32 pads are defined with Pin(Top, SolderMask Top, PasteMask Top).

In the datasheet, it is recommended not to solder Exposed Die pad in the center.

So my question is :is it necessary to define Pin in the same way as i did for the above 32 pads OR can i design it like Pin(Top, SolderMask Top

and do not use PasteMask top as i do not want it to be soldered OR do not define anything for exposed pad at all) on that pad. This is a sensor chip so i would avoid using any copper underneath this sensor.

I have an archived capture design (.DSN) that was sent outside for layout. Once completed the layout (.BRD) was also archived. Both were done with an older version of Cadence/Allegro and the .DSN was never back annotated nor populated with footprints. I'm attempting to update the capture design and back annotate but running into issues. There seems to be a plethora of information, but most seems to older versions of Capture. Can someone offer advice on syncronizing and back annotating the Capture Design file? Thank you in advance.

Concept HDL 17.2

Importing a lower level block loses the reference designators and results in an un-reusable PCB layout. The box for retaining reference designators is selected. Is there an elegant way to revise a complex hierarchical schematic such that the previous PCB file is useful?

Hi guys,

I have a PCB file, and then I open it by Allegro Tool. But, I see a message like this:

This is a first time I met this, I don't know anything about this error, so hope everybody help me! Thanks so much!

Regards

Hello,

I have to manage two board with the same schematic but different BOM.

The two DSN have the same property "NM" for non mounted component, only this column is different on the two designs.

The board is exactly the same, only DSN/BOM are different.

I want to know if there is a way to easily manage this double configuration.

After merging the two schematic, today I proceed this way;

1) I added a "NM_C2" column in the property

2) After I updated the schematic I need to export the BOM twice with "NM" and "NM_C2" configuration.

3) The schematic is not clear because only the property "NM" is displayed, it's not easy to check the "NM_C2" configuration.

Why In the property editor we can't change the display configuration for all components ? Today we need to change the display property one component by one component from the schematic editor ...

Thank you for help.

Regards,

Eliott T.