Hi i am Vos.

When the net schedule is set in the PCB editor and auto-routing is executed, the routing is different from the set schedule.

Is there a solution to this problem?

thanks.

Hi i am Vos.

When the net schedule is set in the PCB editor and auto-routing is executed, the routing is different from the set schedule.

Is there a solution to this problem?

thanks.

The create netlist window doesnt have "Create or update pcb editor board" option. The process stops there and I have no clue how to open my schematic in pcb editor. I am using 17.4 version.

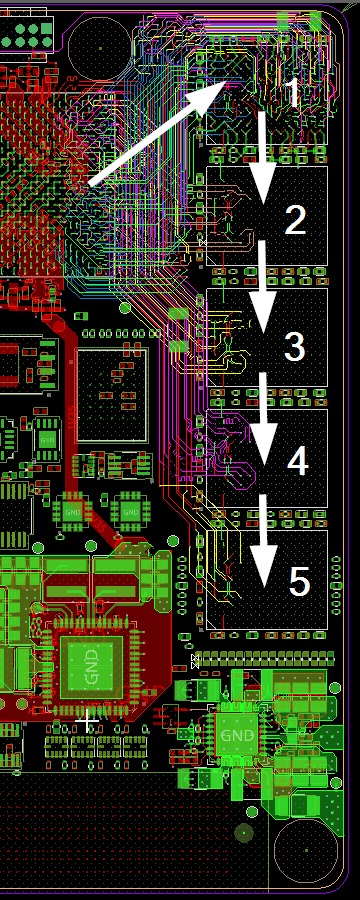

I'm currently working on a project involving routing of DDR4 memory in a fly-by topology. For a fly-by topology, routing needs to be length matched from the controller to the first device in the series, length matched again from the first device to the second, and length matched to the remaining devices in the order they are configured. See the attachment below for a visual.

I'm using the etched length constraint CSet to match the lengths from the controller to the first device. The direct routed current length is 1932 mils with a min/max of 2485/2505 to the first device, so it is much less than the targeted length window. If I tried to delay tune this net to achieve the desired length, the length meter is showing that I am way over my target when it should be under. See the meter below.

If I examine the net using show element, I see that the total etch length (totE) is including the unrouted ratsnests for the DDR4 memory devices that are yet to be routed. See the "Show Element" window below.

And here is my constraint class with the CSet using D1_MACT_B as an example.

So, the actual "Total Etch Length" is 1932 mils, but the total etch length shown when routing is 4143 mils because it is including ratsnest in total etch.

I've submitted a support ticket to EMA-EDA on 8/14, but they have made no progress on a solution.

Now, I can't imaging that I am the first person to implement DDR in a fly-by topology. What tools are available to help length match in this routing method? Am I using the wrong tool? Is there a setting to not include ratsnest in the total etch length?

My tool set is OrCAD PCB Designer Professional 17.4-2019 S009.

After I run data sync, it stucks. I waited for hours but it does not process or ends. What could be wrong with it? I am using orcad 17.4 version

I made a simple design following an instructor course. Here I placed a connector from C:\Cadence\SPB_17.4\tools\capture\library. When I run Launch design sync I get these warnings as mentioned in the subject. One more error in the same session log is #3 ERROR(ORCAP-36002): Property "PCB Footprint" missing from instance J2: LEDPCB, LEDPCB (6.00, 2.10).

I am completely new to orcad. Please help me in sorting it out. Thanks

At my last employer I had a scalpel skill tool that was very handy. Can anyone share this or point me to it?

It allowed you to draw a path across traces and cut them in that location.

Hi,

We are developing a custom component database and a CRUD app to manage the database. We are using multiple CAD-systems and the database is used for all the CAD-systems.

It would be great if it was possible to get a preview of the graphics in an OLB-file and DRA-file to display in the App.

Is there a way to display the graphics in a third party sw or convert the graphics to a bitmap?

Regards,

Marcus

Hello

I usually set relative propagation delay delta tolerance value in mils like “0:100mils” . One of the board I received for modification having it set in “ns” and the max length difference is 311mils , but still its shows green.

Just wanted to know “0.01ns means how much in mils ? ( I consider 140ps = 1000mils , but this doesn’t match with the constraint set in CMGR)

I referred below two document to get the value , but unable to correlate with CMGR value .

Document ref : https://www.flowcad.ch/cms/upload/ApplicationNotes/FlowCAD_AN_PCB_Constraining_Delay_Rules.pdf

Document ref : https://www.eetimes.com/meeting-timing-specs-on-boards-with-picoseconds-of-margin/

I am using 17.2 SO63, when outputting artwork I have unused pad suppression checked, plot mode positive.

My artwork is still putting unused pads on internal layers.

When looking at the pad stack in the pad stack editor I see an option "Supress unconnected internal pads; legacy artwork" (I believe this for older Allegro versions).

I have tried with his both on and off, updated the via but this seems to make no difference; artwork still has pads on unconnected internal pads.

I also notice our library is all over the place. Some have internal pads defined while some just use "Default Internal" does this affect this functionality?...doesn't seem to...

What am I missing? Thanks for any help / ideas.

Hello,

When i generated pdf for my schematic, i observed net alias names were not in aligned with net (you can see image below) . Is any one know, what i am missing in setting up ?

Thanks you in advance.

Could this function "Online DRC" be set as default disable in Capture 17.4?

This will affect the system response.

Thanks.

Hello there,

I am trying to assign a function key in myenv to a right click menu item "edit boundary" when i am editing shapes. The code I did tried was

funckey e "prepopup;pop dyn_option_select '@:@Edit Boundary'"

however this does not seem to work. The best reference I have are snap pick to commands that seem to follow a similar structure. Can anyone help me out?

Thanks!

Best Regards.

In Orcad 17.2, I am using a hierarchal design. In Allegro, I already placed all my connectors. When importing the netlist into allegro, I got a renaming problem.

In Capture, I took off connector J1000 from a page and put it in another page. I did an annotate with Unconditional reference update. It renamed all the connectors again from J1000. In Capture I create, the netlist.

In Allegro, I imported the netlist. I no longer have the correct connectors at the correct locations. I have to interchange several connectors. I don’t know if this always happens. How do I prevent this? I put my annotate settings in the picture below. I won't need unconditional reference all the Dmitri.

Help please,

Frank

Dear Orcad Expert,

I have been an Orcad user for quite a while, but never create or set up a CIS environment. after I set up the CIS step by step, it almost works but the last step, place the Database part.

1.

2. When I setup the CIS configuration, Here is my observation, I know it could be the problem, but need help to solve it.

as shown in the picture, in the configuration table. Table property name is "Schematic Part",

if the Property Type is "normal", I can check the Transfer to Design, and the OrCAD property name will show "Schematic Part" automatically.

if change the Property Type to "Schematic_Part", then the "Transfer to Design" block is disabled. guess something wrong here.

3. but If I click on the schematic, choose a CAP, right-click and choose view database part, I will get some green table like this

please give me some instruction to solve this problem, thanks,

David Sun

Hello everyone. I'm new in cadence products. I wonder if there is a way to solve the following mistake. When I had all the electronic devices placed on the PCB, and I want to route all the tracks but not manually because there are a lot of them, so I try to use the option "Route->PCB router->Route automatically" but cadence throw me a message that disable the "Route" option.

"Please verify that you are running allegro pcb router version V9.0 or later. try "file viewlog" to view Allegro PCB rpouter's log file"

Thanks in advance.

Hi, Orcad Expert,

Our team has a few Eagle design transferred to Orcad independently. Each design will have a .olb library associated with it. these libraries are overlapped for most of the parts. after convert to Orcad, I want to merge these libraries to one OLB file, is there a good strategy to do this kind of house cleaning? high efficient and low error risk.

Thanks for your help.

David Sun

hello

i am using the show measure command consecutively but the persistent snap on segment vertex or any other objects does not work.

the persistent snap does not work on the second time.

Is it only me or some type of bug?

Have the version 17.2 S069 for layout using Windows 10. Want to find out if this is a bug or just something we are missing. Have a board with connectors and on one pin the pour going to the pin is a solid pour (pin is flooded over top and bottom layers) I had a short stub on this pin and after running the report it did not pick up the stub. Before we loaded the latest hot fix it would always catch this type of stub. The picture shows a stub coming from a SMT pad going into a pour that is the same net as the pin. We were using version S060 before and it would flag this type of stub. So if you have spare time could you try to see if it does the same on your version. This might be fixed in 17.4 but we haven't loaded that version yet.

The board in the picture does not flag the stub with our version.

Hello Everyone,

I am using Orcad PCB Designer Standard (version 17.2-2016 S065 [3/16/2020] Windows SPB 64-bit Edition) to design my second board and run into this Thru Pin to Shape DRC. Any help would be very much appreciated.

My board is a 4-layer board (signal/GND plane/PWR plane/signal). Whenever I add a shape (for copper) to enclose a thru-hole part on the inner plane (GND or PWR), I get this DRC on every pin of the part. The copper connects to all the pins and therefore these P/S DRC errors. Yet, when I add a shape in the same way on the outer layers, there is no problem. I did not run into this problem while working on my first board.

I am attaching two screenshots for your review with shape enclosed an 8-pin through-hole terminal block:

- Screenshot 1 with orange shape on the GND plane (with 8 DRC's)

- Screenshot 2 with green shape on the top signal layer (with no DRC)

- Screenshot 3 with green shape on the GND plane of my first board (with no DRC)

Please note that the second board started from scratch and not from the first board design environment/settings. I have checked the "Shape -> Global Dynamic Parameters..." of both files and they are the same.

What seems to be the cause

?. What other areas should I check?. Thanks.

?. What other areas should I check?. Thanks.

TC

Hello everyone.

I created a schematic in Capture and transferred it to the PCB Editor. In the meantime, I've added some elements and when I try to update the netlist I receive a bunch of such errors.

ERROR(SPCODD-409): Error at line 129 while loading the C:\USERS\AAAA\DOCUMENTS\PROJECTS\XYZ\

2020-09-03-1200\allegro\pstxnet.dat file. Unable to create the following new pin instance, 2, as the pin definition was not found.

Reference Designator: J40.

Schematic Instance: @\XYZ.\XYZ\(sch_1):\INS1109293\@\CONNECTOR\.\MC1.5/2-G-3.81.Normal\(chips) (MODULE: XYZ; PART: MC1.5/2-G-3.81).

Check the symbol and ensure that the pin definition is consistent.

I tried to delete them manually from the netlist file and from time to time that seemed to work. But now I'm not capable of neither generating netlist nor updating layout. Additionaly, in PCB Editor when I select the Place Components Manually tool, there are listed many elements I don't have in my schematic anymore?

How can I approach this problem?